참고문헌

[1] Epitaxial graphene growth on silicon carbide, Wikipedia

이번 과제에서 substrate가 SiC위에 graphene을 MBE 성장시킨 기판이길래 정리하고자 합니다.

Thermal deposition을 통해 SiC위에 그래핀을 성장시키는 방법은 large-scale few-layer graphene (FLG)를 만드는데 사용된다. 그래핀은 전도유망한 나노물질 중 하나로, 이는 그래핀의 강력한 stiffness, 그리고 전기전도성, 열 전도도 때문이다. 아직, 그래핀의 복제 가능한 생성은 어려운 형편이며, 수많은 방법들이 개발됐다. 다른 여러 기술들과 비교했을때 SiC위에 epitaxial 그래핀을 성장시키는 것의 주요 이점은 그래핀 layer를 상업적으로 이용 가능한 반도체/또는 반부도체적인 기판 위에 직접적으로 얻을 수 있다는 것이다.

역사

Bulk SiC의 열적 decompisitio은 1965년 Badami에 의해 처음 보고됐다. 그는 진공환경에서 SiC를 2180도 부근에서 약 한시간동안 어닐링 했으며, 이는 graphite lattice를 얻기 위함이었다. nfff

History[edit]

In 1975, Bommel et al. then achieved to form monolayer graphite on the C-face as well as the Si-face of hexagonal SiC. The experiment was carried out under UHV with a temperature of 800 °C and hints for a graphene structure could be found in LEED patterns and the change in the carbon Auger peak from a carbide character to a graphite character. [4] [5] New insights in the electronic and physical properties of graphene like the Dirac nature of the charge carriers, half-integer quantum Hall effect or the observation of the 2D electron gas behaviour were first measured on multilayer graphene from de Heer et al. at the Georgia Institute of Technology in 2004.[6][7] Still, the Nobel Prize in Physics ″for groundbreaking experiments regarding the two-dimensional material graphene″ in 2010 was awarded to Andre Geim and Konstantin Novoselov. An official online document of the Royal Swedish Academy of Sciences about this awarding got under fire. Walter de Heer mentions several objections about the work of Geim and Novoselov who apparently have measured on many-layer graphene, also called graphite, which has different electronic and mechanical properties.[8] Emtsev et al. improved the whole procedure in 2009 by annealing the SiC-samples at high temperatures over 1650 °C in an argon environment to obtain morphologically superior graphene.[9]

Process[edit]

The underlying process is the desorption of atoms from an annealed surface, in this case a SiC-sample. Due to the fact that the vapor pressure of carbon is negligible compared to the one of silicon, the Si atoms desorb at high temperatures and leave behind the carbon atoms which form graphitic layers, also called few-layer graphene (FLG). Different heating mechanisms like e-beam heating or resistive heating lead to the same result. The heating process takes place in a vacuum to avoid contamination. Approximately three bilayers of SiC are necessary to set free enough carbon atoms needed for the formation of one graphene layer. This number can be calculated out of the molar densities.[10] Today's challenge is to improve this process for industrial fabrication. The FLG obtained so far has a non-uniform thickness distribution which leads to different electronic properties. Because of this, there's a demand for growing uniform large-area FLG with the desired thickness in a reproducible way. Also, the impact of the SiC substrate on the physical properties of FLG is not totally understood yet.[1]

The thermal decomposition process of SiC in high / ultra high vacuum works out well and appears promising for large-scale production of devices on graphene basis. But still, there are some problems that have to be solved. Using this technique, the resulting graphene consists of small grains with varying thickness (30–200 nm). These grains occur due to morphological changes of the SiC surface under high temperatures. On the other side, at relatively low temperatures, poor quality occurs due to the high sublimation rate.[2]

The growth procedure was improved to a more controllable technique by annealing the SiC-samples at high temperatures over 1650 °C in an argon environment. [11][9] The desorbed silicon atoms from the surface collide with the argon atoms and a few are reflected back to the surface. This leads to a decrease of the Si evaporation rate.[12] Carrying out the experiment under high temperatures further enhances surface diffusion. This leads to a restructuring of the surface which is completed before the formation of the graphene layer.[2] As an additional advantage, the graphene domains are larger in size than in the initial process (3 x 50 μm2) up to 50 x 50 μm2 .[13] [14]

Of course, the technology always undergoes changes to improve the graphene quality. One of them is the so-called confinement controlled sublimation (CCS) method. Here, the SiC sample is placed in a graphite enclosure equipped with a small leak. By controlling the evaporation rate of the silicon through this leak, a regulation of the graphene growth rate is possible. Therefore, high-quality graphene layers are obtained in a near-equilibrium environment.[7] [15] The quality of the graphene can also be controlled by annealing in the presence of an external silicon flux. By using disilane gas, the silicon vapor pressure can be controlled.[16]

Crystallographic orientation between the SiC and graphene layers[edit]

SiC is bipolar and therefore the growth can take place on both the SiC(0001) (silicon-terminated) or SiC(0001) (carbon-terminated) faces of 4H-SiC and 6H-SiC wafers. The different faces result in different growth rates and electronic properties.

Silicon-terminated face[edit]

On the SiC(0001) face, large-area single crystalline monolayer graphene with a low growth rate can be grown.[7] These graphene layers do have a good reproducibility. In this case, the graphene layer grows not directly on top of the substrate but on a complex (6⋅3×6⋅3)R30∘

structure.[15] This structure is non-conducting, rich of carbon and partially covalently bonded to the underlying SiC substrate and provides, therefore, a template for subsequent graphene growth and works as an electronic ″buffer layer″. This buffer layer forms a non-interacting interface with the graphene layer on top of it. Therefore, the monolayer graphene grown an SiC(0001) is electronically identical to a freestanding monolayer of graphene.[15] Changing the growth parameters such as annealing temperature and time, the number of graphene layers on the SiC(0001) can be controlled .[2] The graphene always maintains its epitaxial relationship with the SiC substrate and the topmost graphene, which originates from the initial buffer layer, is continuous everywhere across the substrate steps and across the boundary between regions with different numbers of graphene layers.[1]

The buffer layer does not exhibit the intrinsic electronic structure of graphene but induces considerable n-doping in the overlying monolayer graphene film.[17] [18] This is a source of electronic scattering and leads therefore to major problems for future electronic device applications based on SiC-supported graphene structures.[19] This buffer layer can be transformed into monolayer graphene by decoupling it from the SiC substrate using an intercalation process.

It is also possible to grow off axis on 6H-SiC(0001) wafers. Ouerghi obtained a perfect uniform graphene monolayer at the terraces by limiting the silicon sublimation rate with N2 and silicon fluxes in UHV at an annealing temperature of 1300 °C.[20]

A growth on the 3C-SiC(111) face is also possible. Therefore, annealing temperatures over 1200 °C are necessary. First, the SiC loses silicon atoms and the top layer rearranges in a SiC(3×3)R30∘

structure. A loss of further silicon atoms leads to a new intermediate distorted stage of SiC(32×3)R30∘

which matches almost the graphene (2 x 2) structure. Losing the residual silicon atoms, this evolves into graphene. The first four layers of cubic SiC(111) are arranged in the same order as SiC(0001) so the findings are applicable to both structures.[2]

Carbon-terminated face[edit]

The growth on the SiC(0001) face is much faster than on the SiC(0001) face . Also the number of layers is higher, around 5 to 100 layers and a polycrystalline nature appear.[10] In early reports, the regions of graphene growths have been described as ″islands″ since they appear on microscopy images as pockets of graphene on the substrate surface.[14][21] Hite et al. however found out, that these islands are positioned at a lower level than the surrounding surface and referred them as graphene covered basins (GCBs). The suggestion is, that crystallographic defects in the substrate act as nucleation sites for these GCBs. During the growth of the graphene layers, the GCBs coalesce with each. Because of their different possible orientations, sizes and thickness, the resulting graphene film contains misoriented grains with varying thickness. This leads to large oriental disorder.[2] Growing graphene on the carbon-terminated face, every layer is rotated against the previous one with angles between 0° and 30° relative to the substrate. Due to this, the symmetry between the atoms in the unit cell is not broken in multilayers and every layer has the electronic properties of an isolated monolayer of graphene.[2]

Evaluation of number of graphene layers[edit]

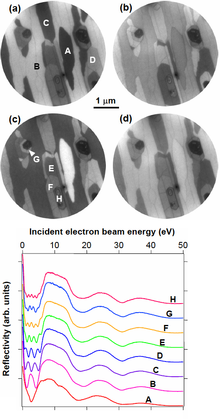

To optimize the growth conditions, it is important to know the number of graphene layers. This number can be determined by using the quantized oscillations of the electron reflectivity. Electrons have a wave character. If they are shot on the graphene surface, they can be reflected either from the graphene surface or from the graphene-SiC interface. The reflected electrons (waves) can interfere with each other. The electron reflectivity itself changes periodically as a function of the incident electron energy and the FLG thickness. For example, thinner FLG provides longer oscillation periods. The most suitable technique for these measurements is the low-energy electron microscopy (LEEM).[1]

A fast method to evaluate the number of layers is using optical microscope in combination with contrast-enhancing techniques. Single-layer graphene domains and substrate terraces can be resolved on the surface of SiC.[23] The method is particularly suitable for quick of the surface.

Applications[edit]

Furthermore, epitaxial graphene on SiC is considered as a potential material for high-end electronics. It is considered to surpass silicon in terms of key parameters like feature size, speed and power consumption and is therefore one of the most promising materials for future applications.

Saturable absorber[edit]

Using a two-inch 6H-SiC wafer as substrate, the graphene grown by thermal decomposition can be used to modulate a large energy pulse laser. Because of its saturable properties, the graphene can be used as a passive Q-switcher.[24]

Metrology[edit]

The quantum Hall effect in epitaxial graphene can serve as a practical standard for electrical resistance. The potential of epitaxial graphene on SiC for quantum metrology has been shown since 2010, displaying quantum Hall resistance quantization accuracy of three parts per billion in monolayer epitaxial graphene.[25] Over the years precisions of parts-per-trillion in the Hall resistance quantization and giant quantum Hall plateaus have been demonstrated. Developments in encapsulation and doping of epitaxial graphene have led to the commercialisation of epitaxial graphene quantum resistance standards

Hall sensors[edit]

Other[edit]

The graphene on SiC can be also an ideal platform for structured graphene (transducers, membranes).[2]

Open problems[edit]

Limitations in terms of wafer sizes, wafer costs and availability of micromachining processes have to be taken into account when using SiC wafers.[2]

Another problem is directly coupled with the advantage. of growing the graphene directly on a semiconducting or semi-insulating substrate which is commercially available. But there's no perfect method yet to transfer the graphene to other substrates. For this application, epitaxial growth on copper is a promising method. The carbon's solubility into copper is extremely low and therefore mainly surface diffusion and nucleation of carbon atoms are involved. Because of this and the growth kinetics, the graphene thickness is limited to predominantly a monolayer. The big advantage is that the graphene can be grown on Cu foil and subsequently transferred to for example SiO2.[26]

See also

'반도체 공정& 소자 > Deposition' 카테고리의 다른 글

| Thin Film (0) | 2024.02.06 |

|---|---|

| Conformality (0) | 2023.05.16 |

| ALD (Atomic Layer Deposition) (0) | 2023.05.04 |

| Chemical Vapor Deposition (0) | 2023.05.04 |

| DIBL (Drain-induced Barrier Lowering) (0) | 2021.05.18 |

댓글